Electrostatic Discharge (ESD) Analysis using SpeedEM: Ensuring Electronic System Reliability – Sigrity – System Analysis

Electrostatic Discharge (ESD) is a common cause of hardware failures in electronic systems. As devices become increasingly complex, the need to address ESD issues at the system level has grown. In this post, we will explore the importance of system-level ESD simulations and how SpeedEM can be used to perform ESD analysis on package designs.

The Need for System-Level ESD Simulations:

Traditionally, ESD protection has been focused on the IC level, with protection diodes and other means used to prevent damage from ESD events during manufacturing and handling. However, as devices become more complex and interconnected, system-level ESD protection mechanisms are needed to handle ESD events in fully operational systems.

IEC-61000-4-2 Standard:

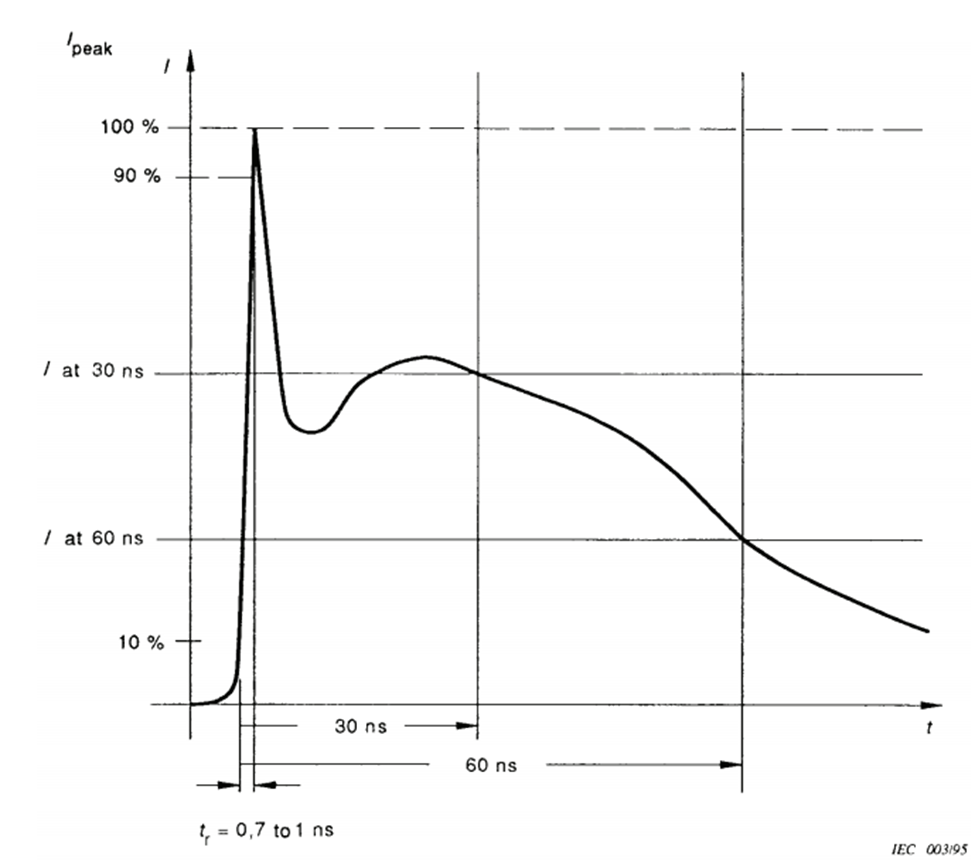

The IEC-61000-4-2 standard defines four levels of ESD protection using two different discharge mechanisms: contact discharge and air discharge. The standard provides a physical test setup and defines a typical discharge event current waveform. This waveform is characterized by a peak current and specific current values at 30ns and 60ns.

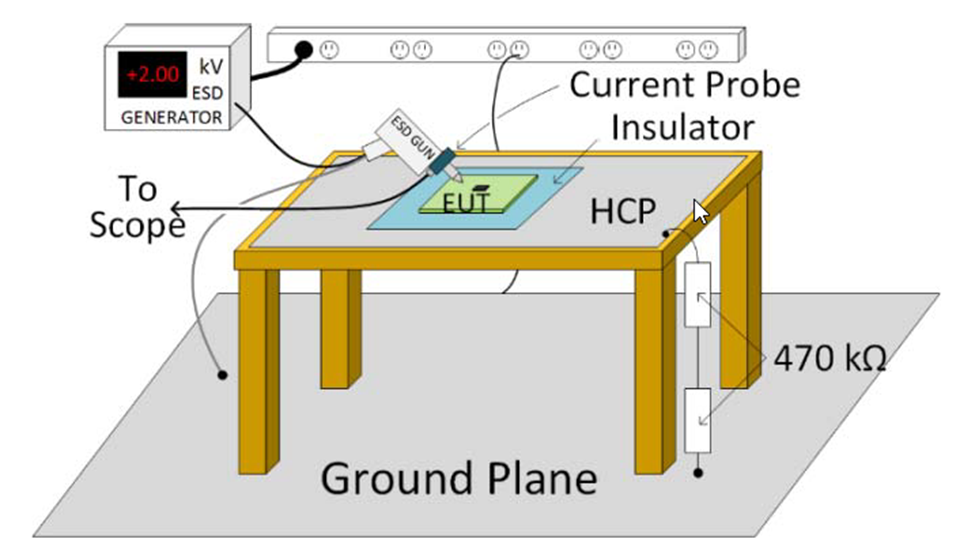

The following image shows the physical test setup defined by the standard:

A typical discharge event produces the following current waveform. In the following image, the peak current is given above, while the current at 30ns and 60ns are also given by the standard:

SpeedEM ESD Analysis:

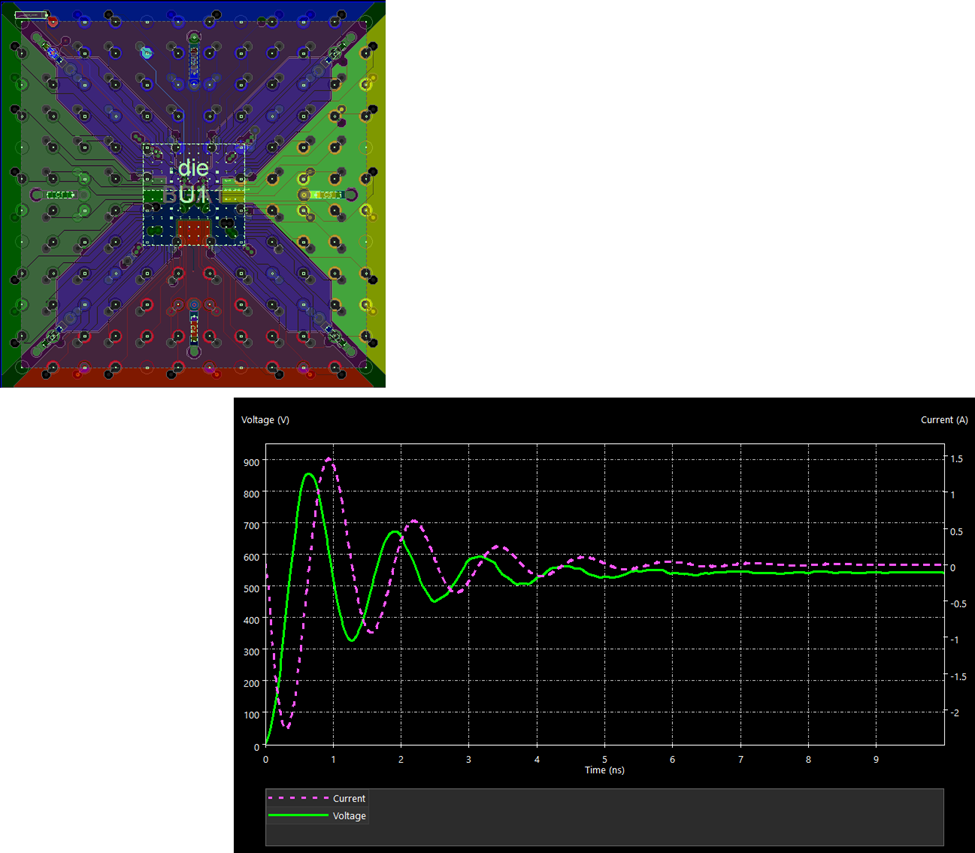

SpeedEM can be used to perform ESD analysis on package designs. The following steps are involved:

- Providing the default ESD gun model circuit: This involves injecting the ESD current into the package design using a default ESD gun model circuit that follows the IEC-61000-4-2 standard.

- Specifying the necessary steps to observe the ESD phenomenon: This involves setting up the simulation to observe the ESD phenomenon on a package design.

Analyzing the ESD waveform: This involves analyzing the ESD waveform to determine the necessary steps to set up ESD protections.

Benefits of SpeedEM ESD Analysis:

Using SpeedEM for ESD analysis provides several benefits, including:

- Early detection of ESD issues: Performing ESD analysis early in the design cycle can help identify potential ESD issues before hardware becomes available.

- Optimization of ESD protections: SpeedEM can be used to optimize ESD protections and ensure that the design meets the required standards.

- Reduced design cycles: By performing ESD analysis virtually, design cycles can be reduced, and the need for physical prototypes can be minimized.

To explore ESD Analysis using SpeedEM, refer to

Electro Static Discharge (ESD) Analysis for Packages with Sigrity SpeedEM

Electrostatic Discharge (ESD) is a significant threat to electronic systems, and system-level ESD simulations are necessary to ensure that designs can withstand ESD events. SpeedEM can be used to perform ESD analysis on package designs, providing early detection of ESD issues, optimization of ESD protections, and reduced design cycles.

Do you have any experience with ESD analysis using SpeedEM? Share your thoughts and experiences in the comments below!

Team SimTech

Cadence Design Systems

Read more here: Source link